# **BSB** – Übung 5: Zeitscheibenscheduling

Yannick Loeck

2022-06-15

#### BSB - HÜ5

Scheduling ohne Kooperation der Threads.

Worum geht es in der Übung heute:

- Konsistenzprobleme beim Scheduling

- Timer-Konfiguration

- Beenden von Threads mit IPIs

Schützen der ready-Liste reicht nicht immer aus

- Schützen der ready-Liste reicht nicht immer aus

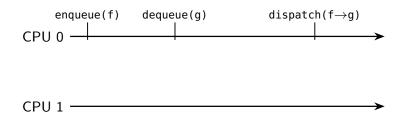

- Mehrere CPUs in resume(): gemeinsame Daten

- Können gleichzeitig Kontext lesen und schreiben

- Einfache Lösung: ganzes resume() Guard-en

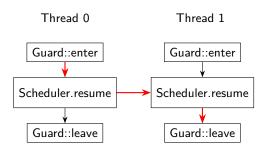

- Schützen der ready-Liste reicht nicht immer aus

- Mehrere CPUs in resume(): gemeinsame Daten

- Können gleichzeitig Kontext lesen und schreiben

- Einfache Lösung: ganzes resume() Guard-en

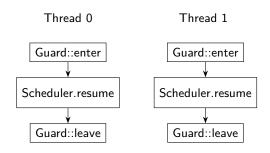

# Thread 0 Thread 1 Guard::enter Scheduler.resume Guard::leave

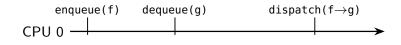

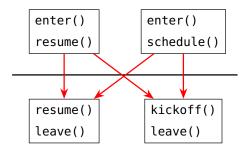

- Scheinbar: enter()  $\rightarrow$  resume()  $\rightarrow$  leave()

- Mitten drin ist aber ein Kontrollflusswechsel

- Scheinbar: enter()  $\rightarrow$  resume()  $\rightarrow$  leave()

- Mitten drin ist aber ein Kontrollflusswechsel

- Wo landen wir auf der anderen Seite?

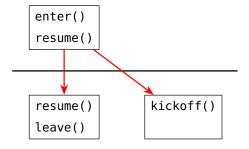

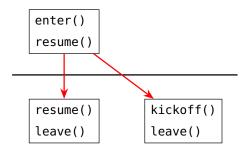

- Scheinbar: enter()  $\rightarrow$  resume()  $\rightarrow$  leave()

- Mitten drin ist aber ein Kontrollflusswechsel

- Wo landen wir auf der anderen Seite?

```

enter()

resume()

resume()

leave()

```

- Alle Kombinationen können auftreten

- Wichtig: enter() und leave() immer paarweise!

- Alle Kombinationen können auftreten

- Wichtig: enter() und leave() immer paarweise!

- Threads rufen Scheduler selbst auf

- Was, wenn nicht?

- System soll periodisch reschedulen ⇒ Timer

- CPU wird dem Thread weggenommen: Preemptive Scheduling

# Timer

- Timer in LAPIC integriert

- Interrupts füllen nicht den Bus

- Alle n ticks ein Interrupt an die CPU

- Timer-Intervall konfigurieren (in StuBS in windup(us))

- Timer an jeder CPU aktivieren (activate())

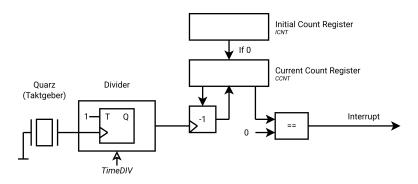

#### APIC-Timer - Aufbau

- Zählt in 32-bit Register (CCNT) runter

- Bei 0: Interrupt, reset auf Wert aus ICNT

- Basis-Clock von außen: APIC Bus Clock

- Überlauf verhindern: Takt wird über Timerdiv geteilt

#### Konfiguration über 4 memory-mapped Register:

- TIMER\_CONTROL: Betriebsmodus, Interrupt-Vektor

- TIMER\_INITIAL\_COUNTER: Initialwert schreiben, Timer stoppt bei 0

- TIMER\_CURRENT\_COUNTER: Aktuellen Wert auslesen

- TIMER\_DIVIDE\_CONFIGURATION: Taktteilung

#### **Achtung**

Reservierte bits im Kontrollregister!

#### Problem 1: Timerdiv einstellen

#### Wir können:

- Taktteiler einstellen

- Timer-Resetwert einstellen

- Timer neu starten

- Überlauf der Register verhindern

- Höherer Timerdiv: Präzisionsverlust

- Ziel: Maximale Präzision für entsprechendes Timer-Intervall

# Problem 2: Was ist überhaupt Zeit?

- Wir arbeiten mit der APIC Bus Clock

- Die kennen wir nicht!

- Kann sogar bei jedem Boot anders sein

# Problem 2: Was ist überhaupt Zeit?

- Wir arbeiten mit der APIC Bus Clock

- Die kennen wir nicht!

- Kann sogar bei jedem Boot anders sein

- Uhr deren Takt wir kennen: Programmable Interval Timer

- Messung zur Umrechnung von Echtzeit zu APIC-Timer-Zeit

- 1. PIT feste Zeitspanne laufen lassen, aktiv auf Ablauf warten

- 2. APIC-Timer währenddessen runterzählen lassen

- 3. Differenz durch Zeitspanne: Takt

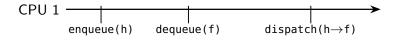

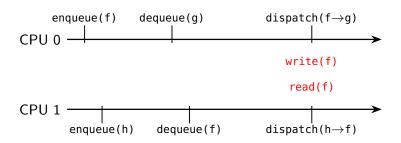

# Assassin

- Bisher: Thread ruft selbst resume() auf, das prüft kill\_flag

- Jetzt: resume() und Überprüfung bei Timer-Interrupt

- Wir wollen Thread sofort beenden, nicht maximal  $\Delta T$  warten

- Lösung: Interrupt an andere CPU schicken

- IRQs jetzt nicht mehr nur von externen Geräten

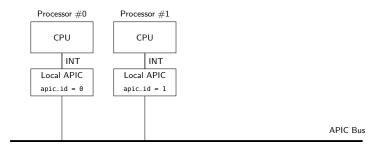

## Inter Processor Interrupt

- LAPICs kommunizieren über Bus auch untereinander

- In StuBS: LAPIC::IPI::send(apic\_id, vector)

- Implementieren im Assassin

#### Es bleiben noch 2 Fragen:

- 1. Warten bis der Thread tatsächlich "tot" ist?

- Wozu jetzt noch das kill\_flag?

### Inter Processor Interrupt

- LAPICs kommunizieren über Bus auch untereinander

- In StuBS: LAPIC::IPI::send(apic\_id, vector)

- Implementieren im Assassin

#### Es bleiben noch 2 Fragen:

- Warten bis der Thread tatsächlich "tot" ist?

Nein, da Scheduler kill und IPI-Epilog beide auf E<sup>1</sup>/<sub>2</sub> sind!

- 2. Wozu jetzt noch das kill\_flag?

#### Inter Processor Interrupt

- LAPICs kommunizieren über Bus auch untereinander

- In StuBS: LAPIC::IPI::send(apic\_id, vector)

- Implementieren im Assassin

#### Es bleiben noch 2 Fragen:

- Warten bis der Thread tatsächlich "tot" ist?

Nein, da Scheduler kill und IPI-Epilog beide auf E<sup>1</sup>/<sub>2</sub> sind!

- Wozu jetzt noch das kill\_flag? Wenn Thread vor Ende von IPI auf andere CPU migriert wird!

- APIC-Timer konfigurieren

- Preemptive Scheduling einführen, Scheduler Guard-en

- MPStuBS: Andere Threads über IPI beenden

#### Hinweise:

- Timer-Interrupt kann jederzeit Threads auf eine andere CPU migrieren: Guard prüfen

- Bei Timer-Berechnung auf Präzision und Integer Overflows achten