**BSB** – Übung 3: Pro-/Epilogmodell

Yannick Loeck

2022-05-11

#### BSB - HÜ3

Interrupts lange sperren erzeugt Latenzen.

Worum geht es in der Übung heute:

- Aufteilen von Interrupt-Behandlung

- Prolog und Epilog

### Probleme bei Harter Synchronisation

#### Main

```

while (1) {

download_more_ram();

print_ram_contents();

}

```

### Probleme bei Harter Synchronisation

```

Main

While (1) {

download_more_ram();

print_ram_contents();

}

on_critical_temp() {

throttle();

print_info();

}

```

Gemeinsame Daten durch Ausgabe

### Probleme bei Harter Synchronisation

```

Main

While (1) {

download_more_ram();

cli();

print_ram_contents();

sti();

}

on_critical_temp() {

throttle();

print_info();

}

```

Problem: Worst Case Execution Time von print\_ram\_contents

### Bessere Lösung

#### Main

```

while (1) {

download_more_ram();

print_ram_contents();

}

```

#### **ISR**

```

prologue() {

throttle();  // HW

return true;

}

epilogue() {

print_info(); // SW

}

```

- Auftrennung der ISR

- Schneller Hardwareteil (jederzeit)

### Bessere Lösung

- Auftrennung der ISR

- Schneller Hardwareteil (jederzeit)

- Langsamer Softwareteil (synchron)

Harte Synchronisation cli, sti

E0 und E1 auf einer CPU

cli, sti Precise IRQ Atomics

Hardware

Harte Synchronisation cli, sti E0 und E1 auf einer CPU

Spinlocks lock, unlock mehrere CPUs

SW Spinlocks

HW cli, sti Precise IRQ Atomics

Hardware

Harte Synchronisation cli, sti E0 und E1 auf einer CPU

Spinlocks lock, unlock mehrere CPUs

|    | Guard: pro/epilogue |             |           |  |

|----|---------------------|-------------|-----------|--|

| SW |                     |             | Spinlocks |  |

| HW | cli, sti            | Precise IRQ | Atomics   |  |

|    | Hardware            |             |           |  |

Harte Synchronisation cli, sti E0 und E1 auf einer CPU

Spinlocks lock, unlock mehrere CPUs

|    | Semaphores  Guard: pro/epilogue |             |           |  |  |

|----|---------------------------------|-------------|-----------|--|--|

|    |                                 |             |           |  |  |

| SW |                                 |             | Spinlocks |  |  |

| HW | cli, sti                        | Precise IRQ | Atomics   |  |  |

|    |                                 | Hardware    |           |  |  |

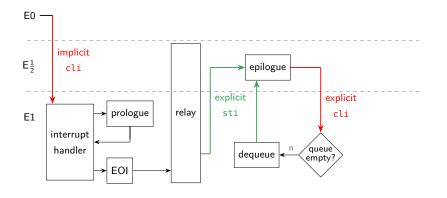

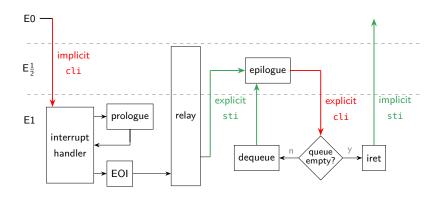

#### **Prolog**

- Von der HW aktiviert

- Interrupts gesperrt

- Latenzreduzierung

- Kann Epilog anfordern

#### **Epilog**

- Folge einer Prologausführung

- Interrupts aktiv

- Ausführung greedy

- Maximal ein Epilog gleichzeitig

- Epiloge auf selber CPU wie Prolog

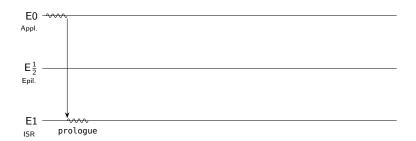

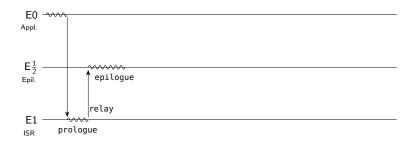

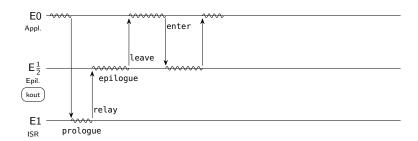

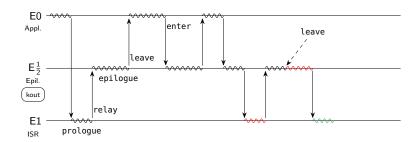

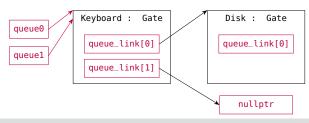

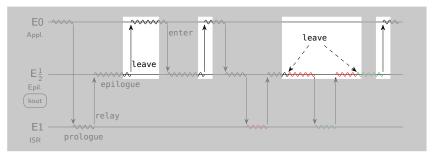

```

E0 \longrightarrow Appl.

E\frac{1}{2} Epil.

E1 ISR

```

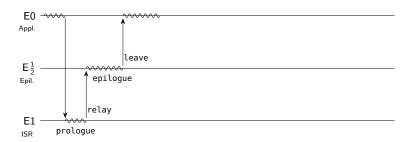

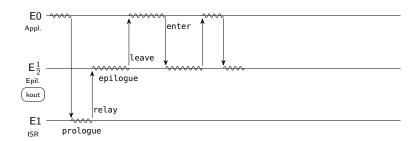

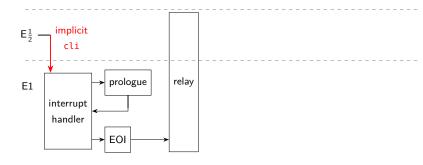

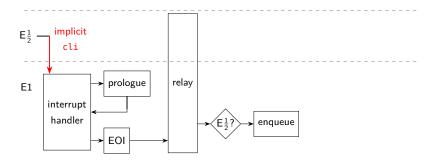

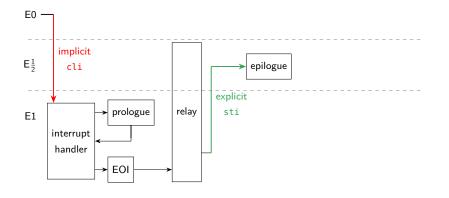

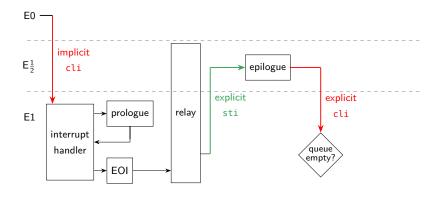

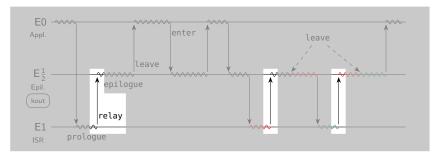

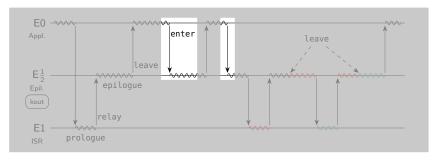

- Anwendungsfluss auf E0

- Prologe (kritischer Teil der ISR) auf E1, Interrupts deaktiviert

- Epiloge (optionaler Rest der ISR) auf E½

- Interrupt: Wechsel auf E1

- interrupt\_handler startet Prolog

- Prolog gibt boolean zurück

- 0: Rückkehr zu E0

- 1: Epilog angefordert, relay

Epilog kehrt mit 1eave zu E0 zurück

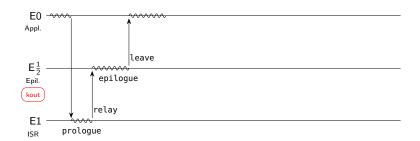

- Kritischen Abschnitt auf E½ verschieben

- kout nur noch auf Epilogebene

- Von E0 zu E½ mit enter

Rückkehr wieder mit leave

- Auf E½ kann Interrupt auftreten

- Laufender kritischer Abschnitt unterbrochen

Ausführung des neuen Prologs

- Unterbrochene Ausführung wird fortgesetzt

- run-to-completion, greedy

- Danach leave

- Prüft ob noch Epiloge da sind und führt sie aus

- Unterbrochene Ausführung wird fortgesetzt

- run-to-completion, greedy

- Danach leave

- Prüft ob noch Epiloge da sind und führt sie aus

- Unterbrochene Ausführung wird fortgesetzt

- run-to-completion, greedy

- Danach leave

- Prüft ob noch Epiloge da sind und führt sie aus

Wenn alle Epiloge fertig sind: Rückkehr zu E0

#### Wir brauchen Funktionen:

relay: Von Prolog zu Epilog

■ enter: Von E0 zu E½

■ 1eave: Verbleibende Epiloge ausführen, zurück zu E0

Und Datenstrukturen:

- Möglichkeit Epiloge zu speichern: Verkettete Liste für Gate-Objekte (pro CPU)

- Unterscheiden ob wir auf E0 oder  $E_{\frac{1}{2}}$  unterbrochen wurden: 1 bit  $E_{\frac{1}{2}}$ -Anzeige (pro CPU)

- (Spin-/Ticket-)Lock, da nur eine CPU gleichzeitig auf E½ sein darf

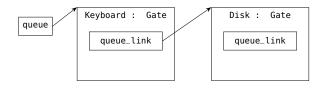

```

Queue < Gate > queue;

queue.enqueue(&Keyboard);

```

- Templated einfach verkettete Liste

- next-Pointer in den Gate-Objekten (kein zusätzliches malloc)

- "Magisches Element": Gate\* queue\_link

- Jedes Element kann also nur ein mal in einer Liste sein

```

Queue < Gate > queue0(0), queue1(1); // MPStuBS

queues [Core::getID()].enqueue(&Keyboard);

```

- Templated einfach verkettete Liste

- next-Pointer in den Gate-Objekten (kein zusätzliches malloc)

- "Magisches Element": Gate\* queue\_link

- Jedes Element kann also nur ein mal in einer Liste sein

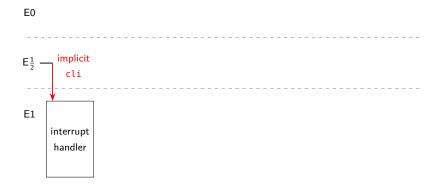

# Funktionen von Guard

| E0                  |      |

|---------------------|------|

|                     | <br> |

| $E^{\frac{1}{2}}$ — |      |

|                     | <br> |

| E1                  |      |

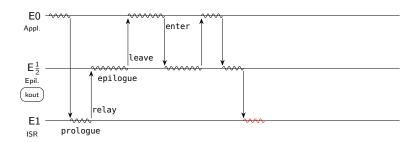

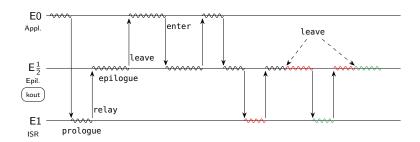

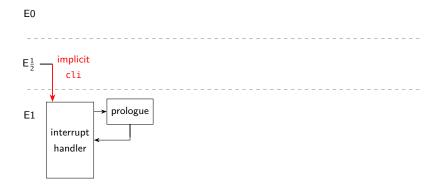

- Auf E0 und E½ sind Interrupts aktiv

- Hier: Interrupt auf E<sup>1</sup>/<sub>2</sub>

Keine Interrupts auf E1

- Handler ruft Prolog auf

- Annahme hier: Epilog angefordert

E0

- Kritischer Teil von Interrupt mit Prolog beendet: EOI

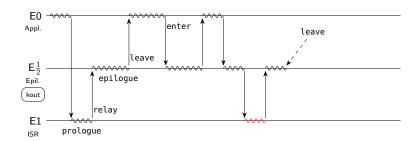

- relay handelt abhängig von unterbrochener Ebene

E0

- Wurde E½ unterbrochen: Epilog in queue einhängen

- Alter Epilog soll erst fortgesetzt werden

- Wurde E0 unterbrochen: Wechsel auf E½

- Ausführung des Epilogs

- E½ kann unterbrochen werden

- Zwischendurch können Interrupts kommen

- Queue prüfen

■ Epiloge aus queue in Schleife ausführen

Queue leer: Wechsel zurück auf E0

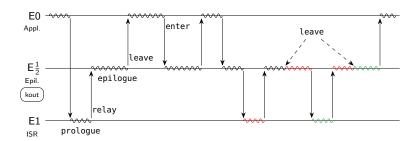

# Guard::relay(Gate\* g)

#### Ebene 1 hat Arbeit für Ebene ½

- Je nach unterbrochener Ebene

- E0: Ebene  $\frac{1}{2}$  betreten, Epilog ausführen

- E½: Epilog in queue einhängen

#### Guard::enter()

#### Wechsel von Ebene 0 auf Ebene $\frac{1}{2}$

- $E_{\frac{1}{2}}$ -Anzeige setzen (auf der aktuellen CPU)

- Lock nehmen

### Guard::leave()

#### Wechsel von Ebene ½ auf Ebene 0

- Epiloge aus der Liste ausführen bis diese leer ist

- E<sup>1</sup>/<sub>2</sub>-Anzeige löschen (auf der aktuellen CPU)

- Lock freigeben

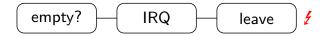

### Problem bei leave

■ Wir prüfen Bedingung und handeln *danach* abhängig vom Wert

- Wir prüfen Bedingung und handeln danach abhängig vom Wert

- Bedingung kann sich dazwischen ändern

- Dann könnte neuer Epilog verloren gehen

#### Lost-Wakeup-Problem

Kann bei Interrupts immer auftreten.

Check und leave muss atomar sein (z.B. Harte Synchronisation)

#### Problem bei leave

- Wir prüfen Bedingung und handeln danach abhängig vom Wert

- Bedingung kann sich dazwischen ändern

- Dann könnte neuer Epilog verloren gehen

#### Lost-Wakeup-Problem

Kann bei Interrupts immer auftreten.

Check und leave muss atomar sein (z.B. Harte Synchronisation)

### Zusatz: Guarded-Objekt

- leave am Ende nicht vergessen

- Guarded kann das erleichtern

- Ruft enter und leave in Konstruktor und Destruktor auf

```

{

enter();

// Code

leave()

}

```

### Zusatz: Guarded-Objekt

- leave am Ende nicht vergessen

- Guarded kann das erleichtern

- Ruft enter und leave in Konstruktor und Destruktor auf

- Resource Acquisition is Initialization

```

{

Guarded g;

// Code

} // Impliziter Destruktor-Aufruf

```

- Gate-Objekte: prologue und epilogue statt trigger

- Interrupt-Handler anpassen

- Guard und Guarded implementieren

- Test-Anwendung von A2 nur noch mit Guarded schützen

#### Achtung

Wenig Code, dafür sehr fehleranfällig.